## EEL 4712: Digital Design

Instructor: Dr. Farimah Farahmandi

## Midterm 1 – 10/2/2019 <u>Time: 55 Minutes</u>

| Name:                                                |                                                                                              |

|------------------------------------------------------|----------------------------------------------------------------------------------------------|

| UFID:                                                |                                                                                              |

| Please be neat and write reasonable effort, it is as | (or draw) carefully. If we cannot read it with a sumed wrong.                                |

| As always, the best answ                             | •                                                                                            |

| , ,                                                  | agree to follow all rules specified below or face                                            |

| receiving a 0% for this ex                           | kam. We will be implementing a Zero-Strike policy.                                           |

| <ul> <li>No electronic devices</li> </ul>            | or printed materials allowed                                                                 |

| <ul> <li>Communication betw</li> </ul>               | veen students is NOT ALLOWED                                                                 |

|                                                      | ces will you share the questions from this test until after nally released by the instructor |

| Re-Grade Information:                                |                                                                                              |

|                                                      |                                                                                              |

|                                                      |                                                                                              |

|                                                      |                                                                                              |

|                                                      |                                                                                              |

|                                                      |                                                                                              |

|                                                      |                                                                                              |

|                                                      |                                                                                              |

|                                                      |                                                                                              |

| Problem | Points | Score |

|---------|--------|-------|

| 1       | 10     |       |

| 2       | 10     |       |

| 3       | 15     |       |

| 4       | 15     |       |

| 5       | 15     |       |

| 6       | 20     |       |

| 7       | 15     |       |

| Total   | 100    |       |

```

ENTITY __entity_name IS

PORT(__input_name, __input_name

: IN STD LOGIC;

: IN STD_LOGIC_VECTOR(__high downto __low);

input vector name

_bidir_name, __bidir_name

: INOUT

STD_LOGIC;

_output_name, __output_name

: OUT

STD LOGIC);

END __entity_name;

ARCHITECTURE a OF __entity_name IS

SIGNAL __signal_name : STD_LOGIC;

SIGNAL __signal_name : STD_LOGIC;

BEGIN

-- Process Statement

-- Concurrent Signal Assignment

-- Conditional Signal Assignment

-- Selected Signal Assignment

-- Component Instantiation Statement

END a:

SIGNAL __signal_name : __type_name;

__instance_name: __component_name GENERIC MAP (__component_par =>__connect_par)

PORT MAP (__component_port => __connect_port,

__component_port => __connect_port);

WITH expression SELECT

signal <= expression WHEN constant value,

__expression WHEN __constant_value,

SELECT assignment statement

__expression WHEN __constant_value,

__expression WHEN __constant_value;

signal <= expression WHEN boolean expression ELSE

Conditional assignment statement

expression WHEN boolean expression ELSE

expression;

IF expression THEN

__statement;

statement;

ELSIF expression THEN

<optional_label>:

__statement;

FOR <loop_id> IN <range> LOOP

-- Sequential Statement(s)

statement;

ELSE

END LOOP:

statement:

statement;

END IF;

WAIT UNTIL expression;

<generate label>:

FOR <loop id> IN <range> GENERATE

CASE __expression IS

-- Concurrent Statement(s)

WHEN __constant_value =>

END GENERATE;

__statement;

_statement;

WHEN __constant_value =>

__statement;

statement:

WHEN OTHERS =>

statement;

statement:

END CASE;

```

1) (10 points) Fill in the waveform for the signals "result\_add" and "result\_sub" in decimal values

```

entity ALU is

port (

clk, rst : in std logic;

input1 : in std_logic_vector(7 downto 0);

input2 : in std logic vector(7 downto 0);

result add, result sub : out std logic vector(7 downto 0);

overflow add : out std logic

);

end ALU;

architecture BHV of ALU is

signal temp Add: std logic vector(8 downto 0);

begin

process(clk, rst)

variable temp sub: std logic vector(8 downto 0);

begin

if(rst = '1') then

result add <= "00000000";

result sub <= "00000000";

overflow add <= '0';

elsif (clk='1' and clk'event) then

temp Add <= std logic vector(unsigned("0" & input1) +</pre>

unsigned("0" & input2));

temp sub:= std logic vector(unsigned("0" & input1) -

unsigned("0" & input2));

result add <= temp Add(7 downto 0);</pre>

result sub <= temp sub(7 downto 0);</pre>

overflow add <= temp Add(8);</pre>

end if;

end process;

end BHV;

Input1

200

81

150

30

110

Input2

100

57

48

20

40

Result_add

X

250

X

1 (overflow)

129

50

Result_sub

10

70

50

143

33

\mathbf{X}

```

b) Explain the behavior of "result\_add's" value, mentioning when signals get updated. Signals are updated at the end of process, variables are updated immediately. Since temp\_Add is defined as a signal, we need two cycles to see the correct value of Result add.

2) (10 points) Identify violations (if any) of the synthesis guidelines for synthesizable logic and the effect on the synthesized circuit.

```

entity test is

port(

input : in std logic vector(3 downto 0);

clk, rst : in std logic;

output : out std logic vector(3 downto 0));

end test;

architecture BHV of test is

begin

process(clk, rst)

begin

Wait/time is not

if (rst = '1') then

synthesizable!

output <= "0000";

elsif(clk'event and clk = '1') then

output = std logic vector(unsigned(input) + 1) after 10ns;

end if;

end process;

process(input)

begin

output <= std logic vector(unsigned(input) + 5);

end process;

end BHV;

Output is derived in

multiple processes

→ Multiple drivers

for a signal

```

3) (15 points) A 16x1 multiplexer is provided as reference. Fill in the code for designing this module using structural descriptions of 4x1 multiplexers and generate statement.

```

entity mux4to1 is

port (w0, w1, w2, w3: in std logic;

s : in std logic vector(1 downto 0) ;

f : out std logic);

end mux4to1;

architecture BHV of mux4to1 is

begin

with s select

f <= w0 when "00",

w1 when "01",

w2 when "10",

w3 when others;

end BHV;

entity mux16to1 is

port (w : in std logic vector(0 downto 15);

s : in std logic vector(3 downto 0);

f : out std logic);

end mux16to1;

architecture STR of mux16to1 is

component mux4to1

port (w0, w1, w2, w3: in std logic;

s : in std logic vector(1 downto 0);

f : out std logic );

end component;

signal m: std logic vector(3 downto 0);

begin

--code to be inserted

MuxGEN: for i in 0 to 3 generate

Muxes: mux4to1 port map

(w0=>w(4*i), w1=>w(4*i+1), w2=>w(4*i+2), w3=>w(4*i+3),

s=>s(1 DOWNTO 0), f=>m(i) );

END GENERATE ;

--code to be inserted

Mux last: mux4to1 port map

(w0=>m(0), w1=>m(1), w2=>m(2), w3=>m(3), s=>s(3) DOWNTO 2),

f=>f );

```

4) (8 points) (a) Define each carry bit of a 4-bit carry lookahead adder (c(1), c(2), c(3), c(4)) in terms of the *propagate* and *generate* functions, and carry in(c(0)).

```

c(1) = g0 + p0 c(0)

c(2) = g1 + p1 c(1) = g1 + p1g0 + p1p0c(0)

c(3) = g2 + p2 c(2) = g2 + p2 g1 + p2 p1g0 + p2p1p0c(0)

c(4) = g3 + p3 c(3) = g3 + p3g2 + p3p2g1 + p3p2p1g0 + p3p2p1p0c(0)

```

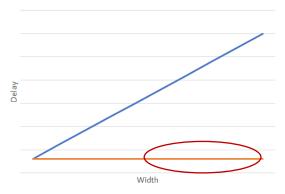

(b) (2 points) Circle the Delay vs width graph that seems appropriate for carry lookahead adder (CLA):

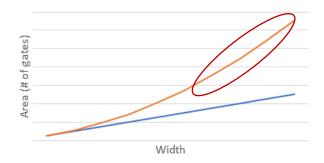

(c) (2 points) Circle the Area (# of gates) vs width graph that seems appropriate for carry lookahead adder (CLA):

(d) (3 points) True/false. A hierarchical carry-lookahead adder reduces area overhead compared to a single-level carry-lookahead adder without increasing propagation delay. False

5) (15 points) Fill in the following behavioral VHDL to implement the illustrated circuit. Assume that clk and rst connect to every register. All wires and operations are width bits. Ignore overflow from the adders.

```

library ieee;

use ieee.std logic 1164.all;

Reg

use ieee.numeric std.all;

add2

reg_add

Mux

entity test1 is

mux_sel

mux_out

generic (width : positive := 8);

Reg

port (

clk, rst, mux_sel : in std_logic;

out1

in1, in2, in3, in 4 : in std logic vector(width-1 downto 0);

out1: out std logic vector(width-1 downto 0));

end test1;

architecture BHV of test1 is

signal reg in2, reg in3, reg in4, add1, add2, add3, reg add, mux out:

std logic vector(width-1 downto 0);

begin

process(clk, rst)

begin

if (rst = '1') then

reg in2 <= (others =>'0');

reg in3 <= (others =>'0');

reg in4 <= (others =>'0');

reg add <= (others =>'0');

out1 <= (others =>'0');

elsif (rising edge(clk))

reg_in2 <= in2;</pre>

reg in3 <= in3;</pre>

reg in4 <= in4;

reg add <= std logic vector(unsigned(reg in3)+unsigned(reg in4));</pre>

if mux sel = '0' then

out1 <= add1;

out1 <= reg add;

end if;

end if;

end process;

add1 <= std logic vector(unsigned(in1) + unsigned(reg in2));</pre>

add2 <= std logic vector(unsigned(add1) + unsigned(reg in3));</pre>

end BHV;

```

in3

Reg

reg\_in3

in4

Reg

reg\_in4

in1

in2

Reg

reg\_in2

- 6) (20 points) Given the following entity definition for a generic adder, Modify the testbench on the next page to:

- (a) To test the "adder" entity as a 32-bit adder.

- **(b)** Make the testbench code <u>general</u>; i.e., can be used to test for any number of bits by changing only the value of **NBITS**.

You need to make all necessary changes to make it work with the generic adder from the previous page (put changes right on the next page)

```

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric std.all;

entity adder tb is

end adder tb;

architecture TB of adder tb is

constant NBITS : positive: 1632;

function X carry test(

signal input1,input2,sum : std_logic_vector(3NBITS-1 downto 0);

constant a, b, c:

signal carry in, carry out : std_logic;

integer)

begin -- TB

return std_logic is

begin

UUT : entity work.adder

if (a + b + c > 15) then

port map (

return '1';

input1

=> A-input1,

else return '0';

input2 => B input2,

end if:

carry in => Carry in,

end X carry test;

sum => + sum, /

function Y (

carry out => E carry out);

constant a, b, c:

integer)

process

return std_logic is

begin

-- function definitions here

return

std_logic_vector(to_unsign

ed(

(a+b-c) mod

16, 4));

end Y;

begin

function Z sum test (

for i in 0 to 15 2**NBITS-1 loop

constant a, b, c:

integer)

for j in 0 to 15 2**NBITS-1 loop

return std_logic_vector

for k in 0 to 1 loop

begin

<= std logic vector(to unsigned(i, 4 NBITS))</pre>

input1

return

input2 <= std_logic_vector(to_unsigned(j, 4 NBITS))</pre>

std_logic_vector(to_unsign

carry_in <= std_logic(to_unsigned(k, 1)(0));</pre>

(a+b+c) mod

wait for 40 ns;

<del>16-</del>2**NBITS, <del>4-</del> NBITS));

end Z-sum_test;

assert(sum = sum test(i,j,k)) report "Sum incorrect";

assert(carry out = carry test(i,j,k)) report "Carry incorrect";

end loop; -- k

end loop; -- j

end loop; -- i

report "SIMULATION FINISHED!";

wait;

end process;

end TB;

```

7) (15 points) Fill in the skeleton code to implement the following Moore finite state machine, using the 2-process FSM model. Assume that if an edge does not have a corresponding condition, that edges always taken on a rising clock edge. Assume that INIT is the start state. Use the next page if extra room is needed.

```

Go= 0

INIT

Count1

Count2

library ieee;

use ieee.std logic 1164.all;

X="00"

X="00"

X="01"

Go= 1

entity fsm is

Done = 0

port (

clk, rst, go, Done : in std logic;

& Go= 0

X : out std logic vector(1 downto 0));

Done=1

GO

DONE

end fsm;

X="11"

X="10"

Done= 0

/Done=1

architecture PROC2 of fsm is

type STATE TYPE is (INIT, COUNT1, COUNT2, DONE, GO);

signal state, next state : STATE TYPE;

begin

process(clk, rst)

begin

if (rst = '1') then

Stata <= INIT;</pre>

elsif (clk'event and clk = '1') then

State <= next state;</pre>

end if;

end process;

process( go, done, state)

begin

next state <= state;</pre>

X \le "00";

Case state is

When INIT =>

Next state <= COUNT1;</pre>

X <= "00";

When COUNT1 =>

If go = '1' then

Next state <= COUNT2;</pre>

End if;

X <= "00";

When COUNT2 =>

Next state <= DONE;</pre>

X <= "01";

When DONE =>

If done = '1' then

Next state <= GO;</pre>

End if;

X <= "10";

```

```

end process;

end PROC2;

```